Page 1 of 2

# 3.2 x 2.5 x 1.0mm 6 pad SMD CMOS

- Frequency range 1.25MHz to 50.0MHz

- CMOS/TTL Output

- Supply Voltage 1.8V, 2.5V, or 3.3V or 5.0VDC

- Integrated Phase Jitter 200fs typical, 1ps max.

- Fundamental mode crystals for best phase noise performance

### SUPPLY VOLTAGE DEPENDENT SPECIFICATION

| Model:                     | 'G' Series                |                              |                              |                                           |  |  |

|----------------------------|---------------------------|------------------------------|------------------------------|-------------------------------------------|--|--|

| Input Voltage:             | Vdd = +1.8VDC±5%          | $Vdd = +2.5VDC \pm 5\%$      | $Vdd = +3.3VDC \pm 5\%$      | $Vdd = +5.0VDC \pm 10\%$                  |  |  |

| Frequency Range*:          | 16.0MHz ~ 50.0MHz         | 1.25MHz ~ 50.0MHz            | 1.25MHz ~ 50.0MHz            | 1.25MHz ~ 50.0MHz                         |  |  |

| Output Wave Form:          | CMOS/TTL                  |                              |                              |                                           |  |  |

| Initial Freq. Accuracy     | Tune with Vc = 0.9V±0.15V | Tune with Vc =<br>1.25V±0.2V | Tune with Vc =<br>1.65V±0.2V | Tune with Vc = 2.5V±0.2V                  |  |  |

| Output Logic High '1'      | 1.62V minimum             | 2.25V minimum                | 2.97V minimum                | 4.5V minimum                              |  |  |

| Output Logic Low '0'       | 0.183V maximum            | 0.25V maximum                | 0.33V maximum                | 0.5V maximum                              |  |  |

| Frequency Deviation Range: | Standard ±80ppm min.      | Standard ±80ppm min.         | Standard ±80ppm min.         | Standard ±80ppm min.<br>±200ppm available |  |  |

| Control Voltage Centre:    | 0.9VDC                    | 1.25VDC                      | 1.65 VDC                     | 2.5 VDC                                   |  |  |

| Control Voltage Range:     | 0.0V to 1.8V              | 0.25V to 2.25V               | 0.3V to 3.0V                 | 0.5V to 1.5V                              |  |  |

#### **GENERAL SPECIFICATION**

Frequency Stability: See table

**Output Load**

TTL: 2 TTL gates CMOS: 15pF

**Rise/Fall Times**

TTL: 6ns max., 4ns typical

Measured between 0.4V to 2.4V

CMOS: 6ns max., 4ns typical

Measured between 20% to 80% of

wave form, (CL = 15pF)

Duty Cycle:  $50\%\pm10\%$  standard,  $50\%\pm5\%$  is

available, add 'S' to part number 200fs typ. 1ps max(12kHz to 20MHz)

Integrated Phase Jitter: 200fs typ. 1ps max(12kHz to Start-up Time: 10ms max., 5ms typical Current Consumption: 10~45mA, freq. dependant

e.g. 27MHz: 10mA @ 3.3V

27MHz: 20mA @5.0V

6% typical, 10% max.

Modulation Bandwidth: 10kHz min. Measured at -3dB with

V control at 1.65V or 2.5V

Input Impedance: 5MΩ typical

Slope Polarity: Monotonic and positive (An

increase of control voltage increases output frequency.)

Ageing: ±3ppm per year max.

Tri-state

Linearity:

Enable high: No connection of VDD-0.5V min. is

applied to Tri-state pin to enable.

Disable: Ground +0.5V max. disables

output. (High impedance)

#### **PHASE NOISE**

Characteristics typical of 27MHz, +3.3V supply.

| Offset | 10Hz | 100Hz | 1 kHz | 10kHz | 100kHz | 1MHz |

|--------|------|-------|-------|-------|--------|------|

| dBc/Hz | -40  | -104  | -132  | -147  | -152   | -150 |

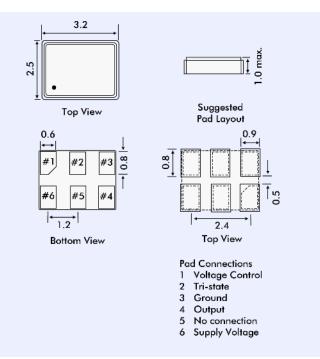

#### **OUTLINE AND DIMENSIONS**

#### FREQUENCY STABILITY OVER TEMPERATURE\*

| Frequency Stability over<br>Operating Temp. Range** | ±25ppm | ±50ppm | ±100ppm |

|-----------------------------------------------------|--------|--------|---------|

| Commercial -10° to +70°C                            | Α      | В      | С       |

| Industrial -40 to +85°C                             | D      | Е      | F       |

<sup>\*</sup> See ordering information

Example:  $C20' = \pm 20$ ppm over -10 to  $\pm 70$ °C

Issue 2

<sup>\*\*</sup> If non-standard temperature stability is required enter the required stability (in ppm) after either 'C' (-10° to +70°) or 'I' (-40° to +85°C)

# 3.2 x 2.5 x 1.0mm 6 pad SMD CMOS

### Page 2 of 2

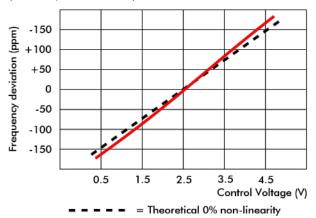

#### TRANSFER FUNCTION

Typical response of 3G326-C-150N-27.000 (at 25°C, positive transfer)

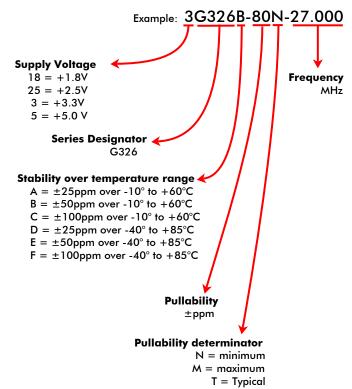

#### **PART NUMBER SCHEDULE**